eGaN® FET DATASHEET EPC2034C

# **EPC2034C – Enhancement Mode Power Transistor**

$V_{DS}$ , 200 V $R_{DS(on)}$  ,  $\, 8\, m\Omega$ I<sub>D</sub>, 48 A

Gallium Nitride's exceptionally high electron mobility and low temperature coefficient allows very low R<sub>DS(on)</sub>, while its lateral device structure and majority carrier diode provide exceptionally low Q<sub>G</sub> and zero Q<sub>RR</sub>. The end result is a device that can handle tasks where very high switching frequency, and low on-time are beneficial as well as those where on-state losses dominate.

|                  | Maximum Ratings                            |            |      |  |  |  |

|------------------|--------------------------------------------|------------|------|--|--|--|

|                  | PARAMETER                                  | VALUE      | UNIT |  |  |  |

| V <sub>DS</sub>  | Drain-to-Source Voltage (Continuous)       | 200        | V    |  |  |  |

|                  | Continuous (T <sub>A</sub> = 25°C)         | 48         | ٨    |  |  |  |

| I <sub>D</sub>   | Pulsed (25°C, T <sub>PULSE</sub> = 300 μs) | 213        | Α    |  |  |  |

| .,               | Gate-to-Source Voltage                     | 6          | V    |  |  |  |

| V <sub>GS</sub>  | Gate-to-Source Voltage                     | -4         | V    |  |  |  |

| T <sub>J</sub>   | Operating Temperature                      | -40 to 150 | ۰c   |  |  |  |

| T <sub>STG</sub> | Storage Temperature                        | -40 to 150 |      |  |  |  |

|                 | Thermal Characteristics                          |     |      |  |  |  |  |

|-----------------|--------------------------------------------------|-----|------|--|--|--|--|

|                 | PARAMETER                                        | TYP | UNIT |  |  |  |  |

| $R_{\theta JC}$ | Thermal Resistance, Junction-to-Case             | 0.3 |      |  |  |  |  |

| $R_{\theta JB}$ | Thermal Resistance, Junction-to-Board            | 4   | °C/W |  |  |  |  |

| $R_{\theta JA}$ | Thermal Resistance, Junction-to-Ambient (Note 1) | 45  |      |  |  |  |  |

Note 1:  $R_{\theta JA}$  is determined with the device mounted on one square inch of copper pad, single layer 2 oz copper on FR4 board. See https://epc-co.com/epc/documents/product-training/Appnote\_Thermal\_Performance\_of\_eGaN\_FETs.pdf for details

| (3) | 9   | 0   | 9   | 9 |

|-----|-----|-----|-----|---|

| (2) | 9   | 9   | 9   | 9 |

|     | 9   | 9   | 9   | 9 |

| 9   | 9   | (2) | 9   | 9 |

| 9   | (3) | 9   | (3) | 9 |

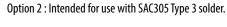

EPC2034C eGaN® FETs are supplied only in passivated die form with solder bumps. Die Size: 4.6 mm x 2.6 mm

- High Frequency DC/DC Conversion

- Multi-level AC/DC Power Supplies

- Wireless Power

- Solar Micro Inverters

- Robotics

- · Class-D Audio

- Low Inductance Motor Drives

| <b>Static Characteristics (</b> $T_j$ = 25°C unless otherwise stated) |                                             |                                                                            |     |       |     |      |  |

|-----------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------|-----|-------|-----|------|--|

|                                                                       | PARAMETER                                   | TEST CONDITIONS                                                            | MIN | TYP   | MAX | UNIT |  |

| $BV_{DSS}$                                                            | Drain-to-Source Voltage                     | $V_{GS} = 0 \text{ V, I}_{D} = 0.6 \text{ mA}$                             | 200 |       |     | V    |  |

| I <sub>DSS</sub>                                                      | Drain-Source Leakage                        | $V_{DS} = 160 \text{ V}, V_{GS} = 0 \text{ V}, T_{J} = 25^{\circ}\text{C}$ |     | 0.03  | 0.4 | mA   |  |

|                                                                       | Gate-to-Source Forward Leakage              | $V_{GS} = 5 \text{ V}, T_J = 25^{\circ}\text{C}$                           |     | 0.002 | 4   | mA   |  |

| $I_{GSS}$                                                             | Gate-to-Source Forward Leakage <sup>#</sup> | V <sub>GS</sub> = 5 V, T <sub>J</sub> = 125°C                              |     | 0.03  | 9   | mA   |  |

|                                                                       | Gate-to-Source Reverse Leakage              | $V_{GS} = -4 \text{ V}, T_{J} = 25^{\circ}\text{C}$                        |     | 0.03  | 0.4 | mA   |  |

| V <sub>GS(TH)</sub>                                                   | Gate Threshold Voltage                      | $V_{DS} = V_{GS}$ , $I_D = 7 \text{ mA}$                                   | 0.8 | 1.1   | 2.5 | V    |  |

| R <sub>DS(on)</sub>                                                   | Drain-Source On Resistance                  | $V_{GS} = 5 \text{ V, I}_{D} = 20 \text{ A}$                               |     | 6     | 8   | mΩ   |  |

| V <sub>SD</sub>                                                       | Source-Drain Forward Voltage                | $I_S = 0.5 \text{ A, V}_{GS} = 0 \text{ V}$                                |     | 1.7   |     | V    |  |

<sup>#</sup> Defined by design. Not subject to production test.

eGaN® FET DATASHEET EPC2034C

|                      | <b>Dynamic Characteristics (</b> $I_J$ = 25°C unless otherwise stated <b>)</b> |                                                                      |     |      |      |          |  |  |  |

|----------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------|-----|------|------|----------|--|--|--|

|                      | PARAMETER                                                                      | TEST CONDITIONS                                                      | MIN | TYP  | MAX  | UNIT     |  |  |  |

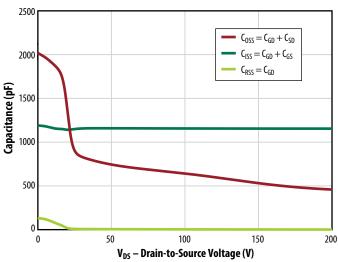

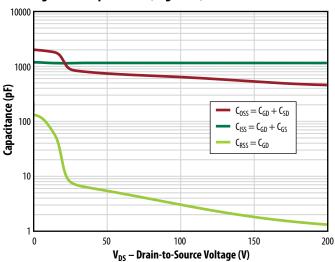

| $C_{ISS}$            | Input Capacitance#                                                             |                                                                      |     | 1155 | 1386 |          |  |  |  |

| $C_{RSS}$            | Reverse Transfer Capacitance                                                   | $V_{DS} = 100 \text{ V}, V_{GS} = 0 \text{ V}$                       |     | 3.1  |      |          |  |  |  |

| C <sub>OSS</sub>     | Output Capacitance#                                                            |                                                                      |     | 641  | 962  | pF       |  |  |  |

| C <sub>OSS(ER)</sub> | Effective Output Capacitance, Energy Related (Note 2)                          | V 04a 100 V V 0 V                                                    |     | 755  |      |          |  |  |  |

| C <sub>OSS(TR)</sub> | Effective Output Capacitance, Time Related (Note 3)                            | $V_{DS} = 0$ to 100 V, $V_{GS} = 0$ V                                |     | 969  |      |          |  |  |  |

| $R_{G}$              | Gate Resistance                                                                |                                                                      |     | 0.5  |      | Ω        |  |  |  |

| $Q_{G}$              | Total Gate Charge <sup>#</sup>                                                 | $V_{DS} = 100 \text{ V}, V_{GS} = 5 \text{ V}, I_{D} = 20 \text{ A}$ |     | 11.1 | 13.8 |          |  |  |  |

| $Q_{GS}$             | Gate to Source Charge                                                          |                                                                      |     | 3.8  |      |          |  |  |  |

| $Q_{GD}$             | Gate to Drain Charge                                                           | $V_{DS} = 100 \text{ V}, I_{D} = 20 \text{ A}$                       |     | 2.0  |      | ]        |  |  |  |

| Q <sub>G(TH)</sub>   | Gate Charge at Threshold                                                       | V <sub>DS</sub> = 100 V, V <sub>GS</sub> = 0 V                       |     | 2.1  |      | nC       |  |  |  |

| Q <sub>OSS</sub>     | Output Charge#                                                                 |                                                                      |     | 96   | 144  |          |  |  |  |

| $Q_{RR}$             | Source-Drain Recovery Charge                                                   |                                                                      |     | 0    |      | <u> </u> |  |  |  |

<sup>#</sup> Defined by design. Not subject to production test.

Note 2:  $C_{OSS(ER)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 50%  $BV_{DSS}$ . Note 3:  $C_{OSS(TR)}$  is a fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 50%  $BV_{DSS}$ .

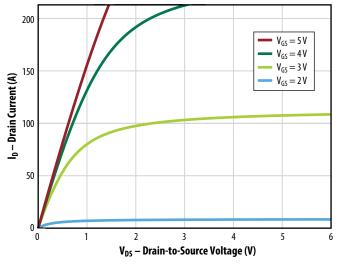

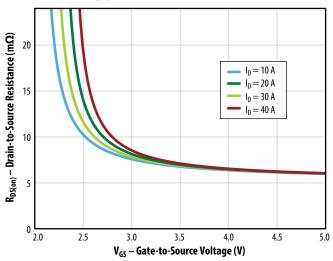

Figure 3:  $R_{DS(on)}$  vs.  $V_{GS}$  for Various Drain Currents

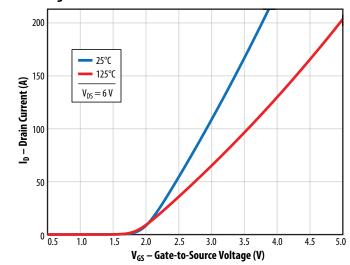

Figure 2: Transfer Characteristics

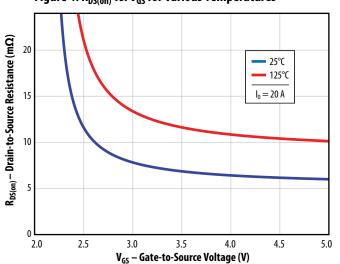

Figure 4: R<sub>DS(on)</sub> vs. V<sub>GS</sub> for Various Temperatures

eGaN® FET DATASHEET EPC2034C

Figure 5b: Capacitance (Log Scale)

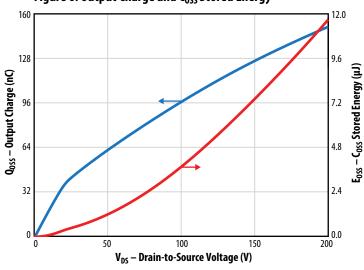

Figure 6: Output Charge and Coss Stored Energy

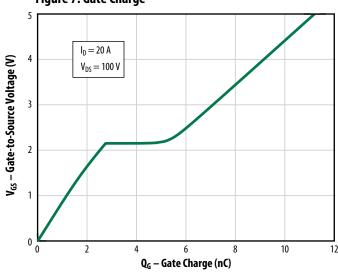

Figure 7: Gate Charge

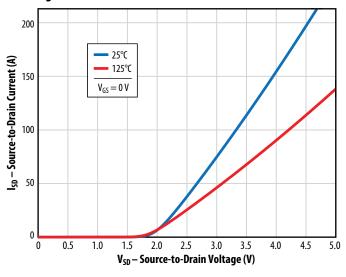

**Figure 8: Reverse Drain-Source Characteristics**

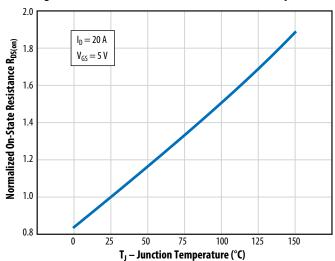

Figure 9: Normalized On-State Resistance vs. Temperature

All measurements were done with substrate shortened to source. T<sub>1</sub>= 25°C unless otherwise stated.

eGaN® FET DATASHEET EPC2034C

Figure 10: Normalized Threshold Voltage vs. Temperature

1.4

1.3

1.2

1.0

1.0

0.9

0.8

0.7

0.6

0 25 50 75 100 125 150

T<sub>J</sub> – Junction Temperature (°C)

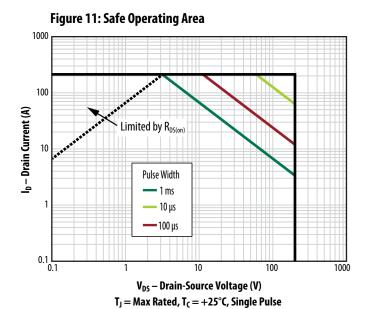

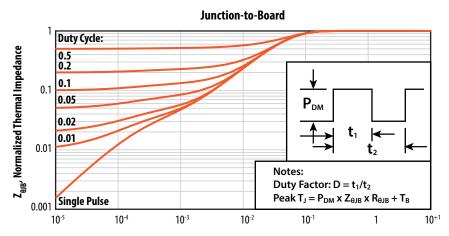

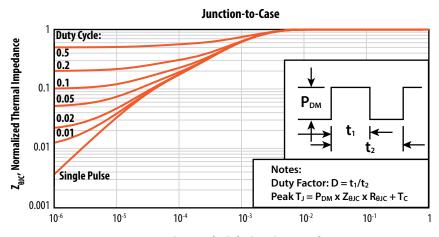

**Figure 12: Transient Thermal Response Curves**

t<sub>p</sub>, Rectangular Pulse Duration, seconds

t<sub>p</sub>, Rectangular Pulse Duration, seconds

EPC2034C eGaN® FET DATASHEET

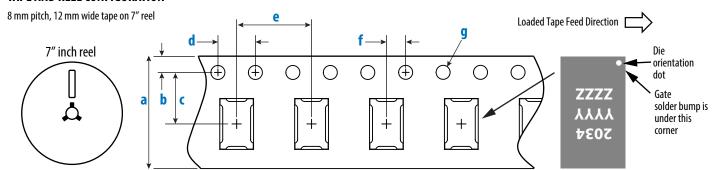

#### TAPE AND REEL CONFIGURATION

|                   | Dimension (mm) |       |       |  |

|-------------------|----------------|-------|-------|--|

| EPC2034C (Note 1) | Target         | MIN   | MAX   |  |

| a                 | 12.00          | 11.90 | 12.30 |  |

| b                 | 1.75           | 1.65  | 1.85  |  |

| <b>c</b> (Note 2) | 5.50           | 5.45  | 5.55  |  |

| d                 | 4.00           | 3.90  | 4.10  |  |

| е                 | 8.00           | 7.90  | 8.10  |  |

| <b>f</b> (Note 2) | 2.00           | 1.95  | 2.05  |  |

| a                 | 1 50           | 1 50  | 160   |  |

Die is placed into pocket solder bump side down (face side down)

Note 1: MSL 1 (moisture sensitivity level 1) classified according to IPC/ JEDEC industry standard.

Note 2: Pocket position is relative to the sprocket hole measured as true position of the pocket, not the pocket hole.

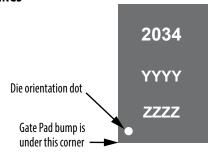

### **DIE MARKINGS**

| Dout           |                          | Laser Markings                  |                                 |

|----------------|--------------------------|---------------------------------|---------------------------------|

| Part<br>Number | Part #<br>Marking Line 1 | Lot_Date Code<br>Marking Line 2 | Lot_Date Code<br>Marking Line 3 |

| EPC2034C       | 2034                     | YYYY                            | ZZZZ                            |

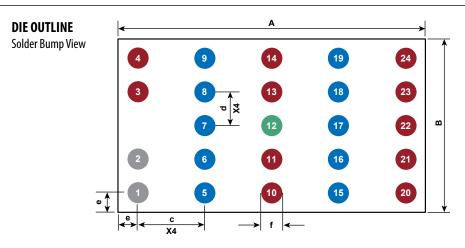

| DIM | Micrometers |         |      |  |  |

|-----|-------------|---------|------|--|--|

| DIM | MIN         | Nominal | MAX  |  |  |

| Α   | 4570        | 4600    | 4630 |  |  |

| В   | 2570        | 2600    | 2630 |  |  |

| C   | 1000        | 1000    | 1000 |  |  |

| d   | 500         | 500     | 500  |  |  |

| e   | 285         | 300     | 315  |  |  |

| f   | 332         | 369     | 406  |  |  |

Pads 1 and 2 are Gate;

Pads 5, 6, 7, 8, 9, 15, 16, 17, 18, 19 are Drain;

Pads 3, 4, 10, 11, 13, 14, 20, 21, 22, 23, 24 are Source;

Pad 12 is Substrate\*

\*Substrate pin should be connected to Source

| ı |  |               | 510 typ  | 790 typ  |

|---|--|---------------|----------|----------|

|   |  | Seating plane | 780+/-28 | <u> </u> |

Side View

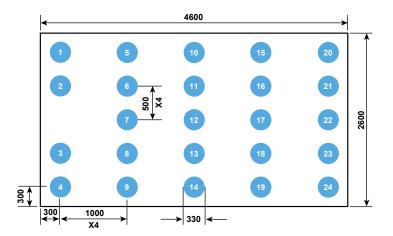

# RECOMMENDED **LAND PATTERN**

(units in  $\mu$ m)

Land pattern is solder mask defined Solder mask opening is 330 µm It is recommended to have on-Cu trace PCB vias

Pads 1 and 2 are Gate;

Pads 5, 6, 7, 8, 9, 15, 16, 17, 18, 19 are Drain;

Pads 3, 4, 10, 11, 13, 14, 20, 21, 22, 23, 24 are Source;

Pad 12 is Substrate\*

\*Substrate pin should be connected to Source

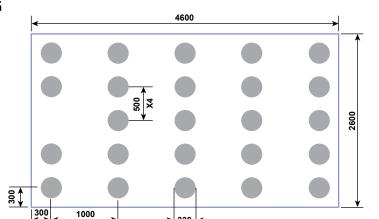

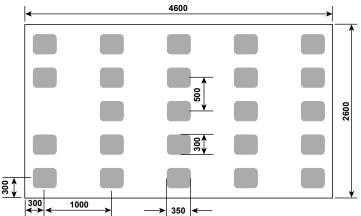

## **RECOMMENDED** STENCIL DRAWING

(units in  $\mu$ m)

Recommended stencil should be 4 mil (100 µm) thick, must be laser cut, openings per drawing.

Additional assembly resources available at https://epc-co.com/epc/DesignSupport/AssemblyBasics.aspx

## **RECOMMENDED** STENCIL DRAWING

(units in  $\mu$ m)

Option 1: Intended for use with SAC305 Type 4 solder.

Recommended stencil should be 4 mil (100 µm) thick, must be laser cut, openings per drawing.

Additional assembly resources available at https://epc-co.com/epc/DesignSupport/AssemblyBasics.aspx

Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein to improve reliability, function or design. EPC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

eGaN® is a registered trademark of Efficient Power Conversion Corporation.

EPC Patent Listing: epc-co.com/epc/AboutEPC/Patents.aspx

Information subject to change without notice. Revised June, 2020